# InP HEMT Cryogenic Ultra-Low Power Low-Noise Amplifiers

Yin Zeng\*(1), Jörgen Stenarson(2), Peter Sobis(1)(2), Niklas Wadefalk(2) and Jan Grahn(1)

(1) Department of Microtechnology and Nanoscience, Chalmers University of Technology SE-412 96 Gothenburg, Sweden

(2) Low Noise Factory AB SE-412 63 Gothenburg, Sweden

#### **Summary**

A cryogenic low-noise amplifier (LNA) based on indium phosphide high electron mobility transistors (InP HEMTs) was designed and fabricated for use in superconducting quantum computing. The three-stage hybrid LNA achieved a noise temperature of 2.8 K (0.04 dB), a gain of 21 dB from 4 to 6 GHz, and a power consumption of only 92  $\mu$ W at 4 K ambient temperature. This design demonstrates a state-of-the-art combination of noise performance with dc power efficiency, making the LNA a suitable choice for future massive qubit systems with the need for many readout amplifiers.

#### 1 Introduction

In recent years, the use of InP HEMT-based cryogenic low-noise amplifiers (LNAs) has become increasingly prevalent in both qubit readout systems and radio astronomy receivers due to their superior noise performance compared to other semiconductor-based LNAs. However, as these systems continue to scale up [1, 2], the power consumption of the cryogenic LNA becomes an increasingly critical issue. Efforts have been made to reduce the power consumption of InP-based cryogenic LNAs while maintaining their noise performance through optimization of the HEMT devices [3]. In this work, a new circuit design is presented that enables a cryogenic LNA to achieve a noise temperature below 3 K from 4 to 6 GHz while consuming only 92  $\mu$ W of DC power. To the best of the authors' knowledge, this represents the lowest noise temperature for a semiconductor-based LNA operating in the sub-100  $\mu$ W power range.

# 2 Cryogenic LNA Design

In this study, a three-stage low-noise amplifier circuit was designed and fabricated using 100 nm gate-length and  $4\times50~\mu$ m gatewidth InP HEMTs in a cascaded common source topology on a 0.381 mm Duroid 6002 substrate with a relative permittivity of 2.94. The circuit was constructed using wire bonding to connect the PCB to the HEMTs mounted on the chassis. The HEMT model was empirically extracted in-house at a 4 K environment. Simulation of both the 3D electromagnetic field and the equivalent HEMT circuit model was performed using a combination of HFSS Ansys and AWR Microwave Office.

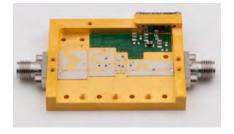

The first and second stage InP HEMT were matched for the best noise performance, whereas the third stage HEMT was matched for the highest gain. A 2 mm deep air chamber was incorporated into the cryogenic circuit chassis to implement a suspended transmission line at the first stage. The suspended transmission line was designed to provide a characteristic impedance of 277  $\Omega$ , which met the high impedance requirement for matching at extremely low power bias. The fabricated circuit was housed in a gold-plated aluminum chassis with SMA coaxial RF connectors and a DC bias circuit, as illustrated in Figure 1.

### 3 Cryogenic LNA Measurement Result

The fabricated LNA was characterized at 4 K for S-parameters, gain and noise. The S-parameters were obtained using a Keysight PNA-X network analyzer. The noise and gain performance was evaluated using an Agilent N8975B noise figure analyzer and the Y-factor method with a 20 dB cold attenuator.

Figure 1. The open structure of the fabricated hybrid cryogenic LNA. The size of the circuit is  $34.9 \text{ mm} \times 42.5 \text{ mm} \times 3 \text{ mm}$ .

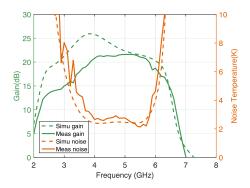

Figure 2. Comparison of measured and simulated gain and noise temperature at 4 K ambient temperature.

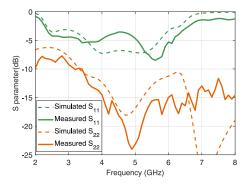

**Figure 3.** Comparison of measured and simulated  $S_{11}$  and  $S_{22}$  at 4 K ambient temperature.

As shown in Figure 2, the simulated and measured noise and gain performance at 4 K were compared and a good agreement was observed. The measured average noise temperature was 2.8 K (0.04 dB) with a gain of 21.0 dB from 4 to 6 GHz while consuming only 92  $\mu$ W dc power at 4 K ambient temperature.

The measured  $S_{11}$  parameter at 4 K was from -8.4 dB to -3.5 dB, with an average value of -4.5 dB, from 4 to 6 GHz, see Figure 3. The measured average  $S_{22}$  parameter was found to be -15.6 dB, which was found to be in agreement with simulation results. The deviation between simulated and measured S11 could be attributed to assembly imperfections and calibration error. It is worth mentioning that since an isolator is typically placed before the HEMT LNA in a qubit read-out chain, the significance of  $S_{11}$  on the overall performance is limited.

#### 4 Conclusion

A hybrid cryogenic LNA for qubit readout was designed and fabricated with a focus on ultra-low DC power operation. The LNA achieved an average noise temperature of 2.8 K (0.04 dB), an average gain of 21.0 dB from 4 to 6 GHz with only 92  $\mu$ W DC power consumption. The significant improvement in DC power consumption compared to current cryogenic LNAs used in quantum computing at 4 K stage makes this design a promising solution for large-scale qubit read-out in future quantum systems.

### References

- [1] IBM, "IBM quantum computer road map," accessed: 2023-01-15. [Online]. Available: https://www.ibm.com/quantum/roadmap

- [2] S. Montazeri, P. K. Grimes, C.-Y. E. Tong, and J. C. Bardin, "A 220-GHz SIS mixer tightly integrated with a sub-hundred-microwatt sige if amplifier," *IEEE Transactions on Terahertz Science and Technology*, vol. 6, no. 1, pp. 133–140, 2015.

- [3] E. Cha, N. Wadefalk, G. Moschetti, A. Pourkabirian, J. Stenarson, and J. Grahn, "InP HEMTs for sub-mW cryogenic low-noise amplifiers," *IEEE Electron Device Letters*, vol. 41, no. 7, pp. 1005–1008, 2020.